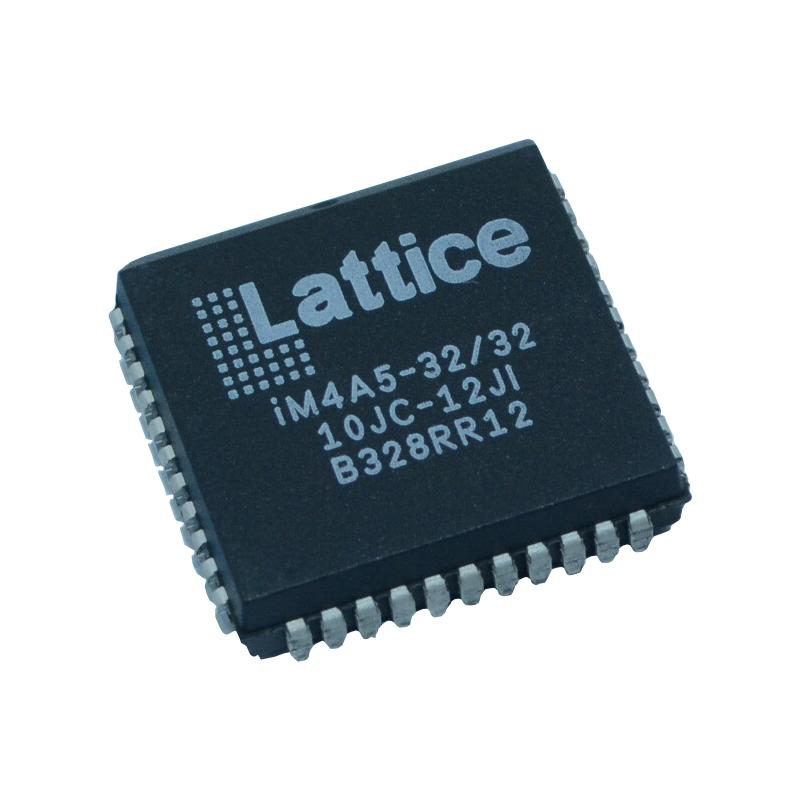

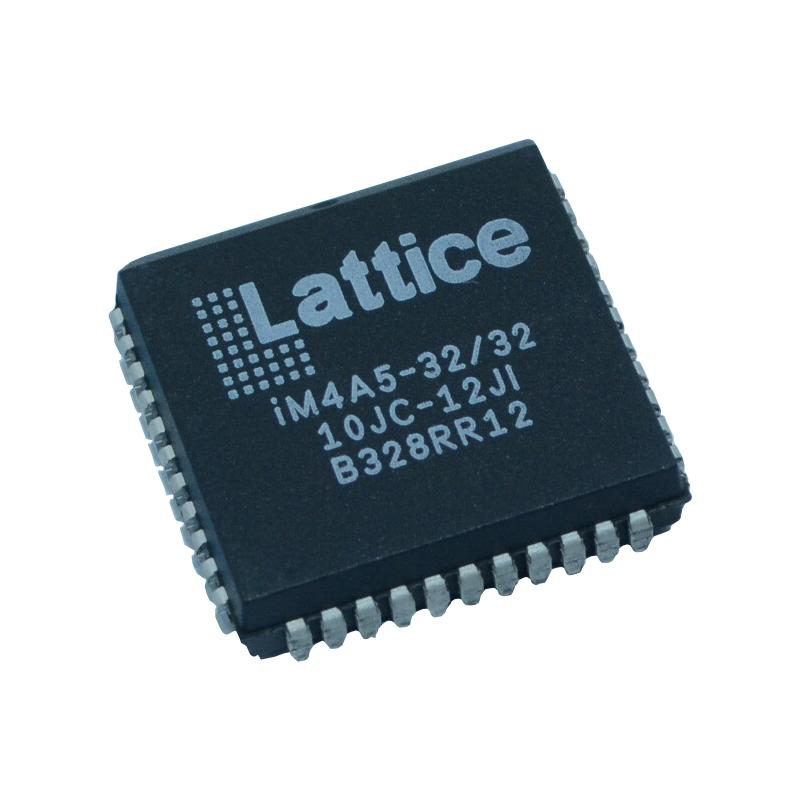

Lattice Semiconductor

M5LV-512/120-6YC

FPGAs (Field Programmable Gate Array)

M5LV-512/120-6YC

2-M5LV-512/120-6YC

CPLD MACH 5 Family 20K Gates 512 Macro Cells 111MHz/167MHz 3.3V 160-Pin PQFP Tray

In Stock : Please Submit RFQ TO US

Not available

QUICK RFQ

ADD TO RFQ LIST

M5LV-512/120-6YC Description

Tech Specifications

Mounting Style

SMD/SMT

Delay Time

6.5 ns

Memory Type

EEPROM

Supply Voltage - Min

3 V

Minimum Operating Temperature

0 C

Number of Macrocells

512

Package / Case

PQFP-160

Operating Supply Voltage

3.3 V

Packaging

Tray

Number of Product Terms per Macro

32

Maximum Operating Frequency

125 MHz

Number of Programmable I/Os

48

Maximum Operating Temperature

+ 70 C

Supply Voltage - Max

3.6 V

Factory Pack Quantity

120

M5LV-512/120-6YC Documents

Download datasheets M5LV-512/120-6YC

Shopping Guide

Payment Methods

Payment_desc

Shipping Rate

Shipping_rate_desc

Delivery Methods

Delivery_Methods_desc