Wie funktioniert JTAG bei FPGAs?

blog_detail_desc

JTAG (Joint Test Action Group), definiert durch den IEEE 1149.1 Standard, ist eine serielle Schnittstelle, die hauptsächlich für Test-, Programmier- und Debugging-Zwecke bei digitalen Geräten – insbesondere bei FPGAs – verwendet wird.

Grundlegende JTAG-Signale

Typische JTAG-Signale bei FPGAs:

| Signal | Name | Funktion |

|---|---|---|

| TCK | Test Clock | Takt zur Synchronisation der Daten |

| TDI | Test Data In | Eingangsdaten für die JTAG-Kette |

| TDO | Test Data Out | Ausgangsdaten aus der JTAG-Kette |

| TMS | Test Mode Select | Steuert den JTAG-Zustandsautomaten |

| TRST (optional) | Test Reset | Optionales Reset-Signal für den TAP-Controller |

Typische Verwendungen von JTAG bei FPGAs

-

Geräteprogrammierung (Konfiguration)

-

JTAG wird oft verwendet, um den Bitstream (.bit oder .svf-Datei) in:

-

Flüchtige, SRAM-basierte FPGAs (z. B. Xilinx, Intel)

-

Nichtflüchtigen Konfigurations-Flashspeicher, der mit dem FPGA verbunden ist, zu laden.

-

-

-

Boundary-Scan-Test

-

Ermöglicht das Testen von Leiterplattenverbindungen ohne physisches Probing.

-

Hilfreich zur Fehlerdiagnose wie Kurzschlüsse, Unterbrechungen oder defekte IO-Pins.

-

-

In-System-Debugging

-

Tools wie Xilinx Vivado oder Intel Quartus nutzen JTAG für:

-

Echtzeit-Hardware-Debugging

-

Überwachung interner Signale mittels SignalTap, ILA (Integrated Logic Analyzer) oder Virtual I/O

-

Lese-/Schreibzugriffe auf interne Speicher, Register oder Logik

-

-

-

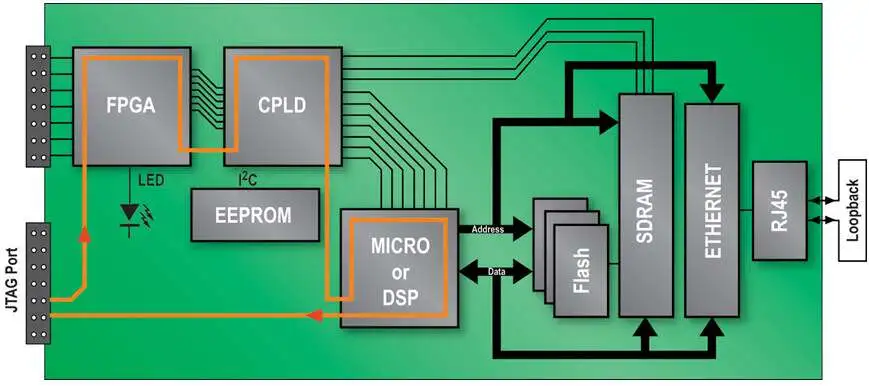

Mehrere Geräte in einer Kette

-

Geräte (FPGAs, CPLDs, Flash, etc.) werden in einer JTAG-Kette hintereinandergeschaltet.

-

Jedes Gerät besitzt eine eigene Instruction Register (IR)-Länge und wird mit gerätespezifischen Befehlen adressiert.

-

JTAG-Zustandsautomat (State Machine)

JTAG funktioniert über einen endlichen Zustandsautomaten namens TAP (Test Access Port) Controller, der Zustände wie folgende durchläuft:

-

Test-Logic-Reset

-

Run-Test/Idle

-

Shift-IR / Shift-DR (Ein-/Ausschieben von Instruktionen/Daten)

-

Update-IR / Update-DR

Die Zustandsübergänge werden durch Kombinationen aus TMS- und TCK-Signalen gesteuert.

Vorteile bei der FPGA-Entwicklung

-

Nicht-invasiv: Kein physischer Zugriff auf interne Pins oder Busse nötig

-

Vielseitig: Für Programmierung und Live-Debugging nutzbar

-

Standardisiert: Unterstützt von fast allen großen FPGA-Herstellern

Beispiel: JTAG-Programmierablauf

-

Anschluss eines JTAG-Programmers (z. B. Xilinx Platform Cable, USB Blaster)

-

Laden des Bitstreams mit einem Tool wie Vivado oder Quartus

-

Serielle Datenübertragung via TDI

-

Konfigurationsspeicher des FPGAs wird aktualisiert

-

TDO sendet Status-/Bestätigungsdaten zurück

Related_Articles

- ·Anwendung von Differenzkristalloszillatoren auf Hochgeschwindigkeits-FPGAs

- ·Wie werden FPGAs in AI/ML Anwendungen eingesetzt?

- ·Anwendung von Embedded Systems in Industrierobotern

- ·Was ist der Unterschied zwischen Zybo-Boards und FPGAs? Und wann werden sie verwendet?

- ·Was sind die am häufigsten verwendeten Chips in der Embedded-Entwicklung?

- ·Können FPGAs GPUs bei der Beschleunigung von Deep Neural Networks der nächsten Generation übertreffen?

- ·Diskussion über die Anwendung von FPGA in der Videokodierung