Was sind die Unterschiede zwischen ARM Cortex-A, Cortex-R und Cortex-M?

blog_detail_desc

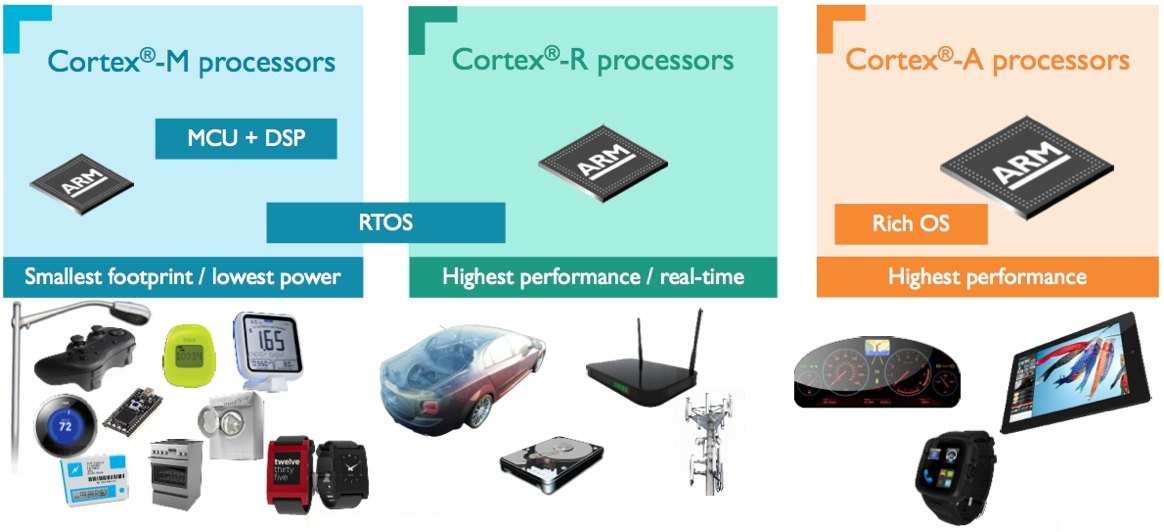

Dies ist eine grundlegende Frage beim Verständnis der ARM-Architektur. Einfach ausgedrückt, entwirft ARM drei verschiedene CPU-Familien für drei grundverschiedene Aufgaben:

-

Cortex-A: Anwendungs-Prozessoren für funktionsreiche Betriebssysteme (Linux, Android, Windows).

-

Cortex-R: Echtzeit-Prozessoren für zeitkritische Aufgaben.

-

Cortex-M: Mikrocontroller-Prozessoren für stromsparende Steuerungsaufgaben.

Im Folgenden finden Sie eine detaillierte Vergleichstabelle und eine tiefergehende Erklärung für jede Familie.

Cortex-A vs. Cortex-R vs. Cortex-M

| Aspekt | Cortex-A (Anwendungsprozessor) | Cortex-R (Echtzeit) | Cortex-M (Mikrocontroller) |

|---|---|---|---|

| Hauptziel | Hohe Performance für Rich-OS & Apps | Harte Echtzeit + funktionale Sicherheit | Niedrigste Leistungsaufnahme, Kosten und Komplexität |

| Typisches OS | Linux/Android, vollständige POSIX-Stacks | RTOS (FreeRTOS, AUTOSAR Classic, SafeRTOS), teils Bare-Metal | Bare-Metal oder kleines RTOS (FreeRTOS, Zephyr, RTX) |

| ISA/Profil(e) | ARMv7-A / ARMv8-A (A32/T32; AArch64 bei v8-A) | ARMv7-R / ARMv8-R (A32/T32) | ARMv6-M / v7-M / v8-M (meist T32/Thumb-2) |

| Speichersystem | MMU erforderlich → volle virtuelle Speicherverwaltung, Prozesse | MPU + Caches + TCM für deterministischen Hot-Code/-Daten | Optionale MPU, einige M-Cores mit TCM (z. B. M7); einfache Busse |

| Latenz/Determinismus | Auf Durchsatz optimiert; Caches/VM & Linux erzeugen Jitter | Für vorhersagbar niedrige Latenz ausgelegt; Cache-Partitionierung/Lockstep | Sehr schneller Interrupt-Eintritt mit NVIC & Tail-Chaining; guter Determinismus |

| Mehrkern/SMP | Häufig; kohärente L1/L2, big.LITTLE, Virtualisierung | Oft Dual-Core mit Lockstep; SMP weniger üblich | Meist Single-Core; einige Dual-Core-MCUs existieren |

| DSP/SIMD | NEON (sowie SVE/SVE2 bei neueren A) | Begrenztes DSP (kein NEON) | Optionale FPU; Helium/MVE bei Cortex-M55/M85 |

| Sicherheit | TrustZone-A, Virtualisierung, umfangreiche Kryptofeatures | Safety + MPU; Security eher systemseitig | TrustZone-M bei v8-M (z. B. M23/M33/M55/M85) |

| Durchsatz & Takte | Am höchsten; skaliert bis Multi-GHz mit OoO-Pipelines | Mittel bis hoch; für Echtzeit bei einigen 100 MHz optimiert | Niedrig bis mittel; einige 10 bis wenige 100 MHz (prozessabhängig) |

| Funktionale Sicherheit | Häufig mit externen Safety-Inseln | Zielklassen ASIL-B/D, SIL 2/3; ECC, Parität, Lockstep (z. B. R5/R52) | Teilweise ASIL-/IEC-zertifiziert; einfachere Safety-Cases |

| Einsatzfelder | Smartphones, HMIs, Gateways, Edge-AI mit Linux, Networking | Automotive-Steuergeräte/ADAS-MCUs, Motorantriebe, HDD/SSD-Controller | Kleine IoT-Knoten, Sensorik, Wearables, einfache Motorsteuerung, Haushaltsgeräte |

| Beispiel-Cores | A53, A72, A76, A78, X-Serie | R5, R52 | M0+, M3, M4, M7, M23/M33, M55/M85 |

Detaillierte Erklärung jeder Familie

1. Cortex-A (Application / Anwendung)

Das "A" steht für "Application" (Anwendung) oder "Advanced". Dies sind die Kerne, die man in Geräten findet, bei denen man mit einem Bildschirm interagiert und ein vollwertiges Betriebssystem verwendet.

-

Schlüsselmerkmal: Memory Management Unit (MMU). Die MMU ist entscheidend für virtuellen Speicher, der ein Betriebssystem wie Linux oder Android in die Lage versetzt, mehrere Anwendungen gleichzeitig in geschützten Speicherbereichen auszuführen. Dies ermöglicht Multitasking.

-

Komplexe Pipeline: Cortex-A-Kerne haben anspruchsvolle Pipelines mit Merkmalen wie "Out-of-Order"-Ausführung und spekulativer Verzweigung, um die Leistung für allgemeine Rechenaufgaben zu maximieren.

-

Einsatzgebiete: Smartphones (die Haupt-CPU in Ihrem Telefon), Tablets, Smart TVs, Einplatinencomputer (wie Raspberry Pi 4), Netzwerkgeräte und sogar Server und Laptops (Apples M-Serie Chips basieren auf einer ARM-Architektur, die Cortex-A ähnelt).

2. Cortex-R (Real-Time / Echtzeit)

Das "R" steht für "Real-Time" (Echtzeit). Diese Kerne sind für Aufgaben konzipiert, bei denen eine versäumte Frist einem Versagen gleichkommt. Die Hauptanforderung ist nicht rohe Geschwindigkeit, sondern Determinismus – die Garantie, dass ein Vorgang in einer genau vorhersagbaren Zeit abgeschlossen wird.

-

Schlüsselmerkmal: Hohe Zuverlässigkeit und niedrige Latenz. Cortex-R-Kerne haben oft Funktionen wie "Dual-Core Lock-Step". Dabei führen zwei identische Kerne die gleichen Befehle parallel aus und vergleichen die Ergebnisse. Bei einer Abweichung (z.B. durch einen Soft Error) kann das System sofort reagieren. Dies ist für sicherheitskritische Systeme unerlässlich.

-

Memory Protection Unit (MPU): Statt einer vollständigen MMU verwenden sie eine MPU. Eine MPU verwaltet keinen virtuellen Speicher, kann aber strenge Speicherzugriffsregeln durchsetzen, um zu verhindern, dass ein Prozess einen anderen abstürzt, und so die Systemintegrität gewährleisten.

-

Einsatzgebiete:

-

Automobil: Elektrische Servolenkung, Antiblockiersystem (ABS), Airbag-Steuerung.

-

Speicher: Der Controller in einer SSD oder Festplatte, der das Lesen/Schreiben von Daten verwaltet.

-

Industrie: Speicherprogrammierbare Steuerungen (SPS) und Robotik.

-

Medizin: Infusionspumpen und Herzschrittmacher.

-

3. Cortex-M (Microcontroller)

Das "M" steht für "Microcontroller". Dies sind die verbreitetsten und kleinsten ARM-Kerne. Sie sind dafür konzipiert, in Mikrocontroller (MCUs) integriert zu werden – einzelne Chips, die eine CPU, Speicher (RAM/Flash) und Peripherie (GPIO, UART, I2C, etc.) in einem Gehäuse vereinen.

-

Schlüsselmerkmal: Extrem niedriger Stromverbrauch und Kosten. Die Philosophie ist maximale Effizienz. Der Befehlssatz (Thumb/Thumb-2) ist sehr kompakt, was die Code-Größe reduziert und kleineren, günstigeren Speicher ermöglicht.

-

Nested Vectored Interrupt Controller (NVIC): Dies ist ein Markenzeichen der Cortex-M-Familie. Sie ermöglicht eine extrem schnelle und vorhersagbare Behandlung von Interrupts, was für die Reaktion auf externe Ereignisse (wie einen Tastendruck) ohne großen Software-Overhead essentiell ist.

-

Einfachheit: Sie haben eine viel einfachere Pipeline (in-order) und sind oft so klein, dass Dutzende von ihnen auf einem einzelnen Chip untergebracht werden können (z.B. zur Verwaltung verschiedener Funktionen in einem großen SoC).

-

Einsatzgebiete: Die riesige Welt der eingebetteten Elektronik. IoT-Geräte (Temperatursensoren, smarte Lampen), Wearables (Fitness-Tracker), Konsumelektronik (Fernbedienungen, Spielzeug), Motorsteuerungen und vieles mehr. Chips von STMicroelectronics (STM32), NXP (Kinetis, LPC) und Texas Instruments (MSP432) basieren auf Cortex-M-Kernen.

Wann welchen Kern wählen?

-

Cortex-A wählen, wenn Sie ein Rich-OS (Linux/Android), User-Space-Prozesse, viel Speicher, Dateisysteme, Netzwerk-Stacks, Browser/UI, hohe Rechenleistung (NEON/SVE) oder Virtualisierung/Container am Edge benötigen.

-

Cortex-R wählen, wenn harte Echtzeit und Safety (ASIL, SIL) entscheidend sind – mit Features wie TCM, Cache-Kontrolle/-Partitionierung, ECC und Lockstep; typisch in Automotive und Storage.

-

Cortex-M wählen, wenn sehr niedrige Leistungsaufnahme, kleiner BOM und Einfachheit im Vordergrund stehen, mit schneller Interrupt-Reaktion, unkompliziertem Bare-Metal/RTOS. Für Signalverarbeitung/ML im MCU-Bereich auf M4/M7 (DSP/FPU) bzw. M55/M85 (Helium) achten.

Kurznotizen & Stolperfallen

-

MMU vs. MPU: A-Profile nutzen eine MMU für virtuelle Speicherverwaltung → zwingend für Linux. R/M verwenden MPUs für regionsbasierte Isolation (geringerer Overhead, keine VM).

-

Interrupts: A verwendet einen GIC (mehr Software-Overhead); M nutzt den NVIC mit Tail-Chaining (sehr schnell); R zielt auf deterministische Latenz mit Vektorisierung und TCM.

-

Vektor/AI: A bietet NEON/SVE; M55/M85 bringen Helium (MVE) für MCU-klassige Vektor-DSP/ML; R bleibt bei skalarem Code + DSP-ähnlichen Instruktionen für Vorhersagbarkeit.

-

Safety-Tooling: R-Profile werden oft mit Safety-Manual, FMEDA und Diagnose-Features (ECC, PBIST/LBIST, Lockstep) geliefert. Viele M-MCUs bieten ebenfalls ECC und Safety-Packages, doch für ASIL-D ist R meist die erste Wahl.

Zusammenfassung

-

Cortex-A (Anwendungsprozessor): Ausgerichtet auf hohe Leistung und Linux/Android; benötigt MMU, unterstützt NEON/SVE, häufig mehrkernig mit Cache-Kohärenz. Geeignet für HMI, Gateways, Edge-Compute.

-

Cortex-R (Echtzeit): Für harte Echtzeit & funktionale Sicherheit; MPU + TCM (vorhersagbar), ECC/Lockstep etc.; üblich in Kfz-Steuerungen, Antrieben, Speicher-Controllern; erleichtert ASIL/SIL.

-

Cortex-M (Mikrocontroller): Für niedrige Leistungsaufnahme/Kosten und schnelle Interrupt-Reaktion; läuft oft Bare-Metal oder mit kleinem RTOS; High-End-Varianten (M55/M85) mit Helium-Vektorerweiterung; ideal für IoT, Sensorik, leichte Regel-/Signalverarbeitung.

Related_Articles

- ·Wie verwendet man ein Kameramodul mit einem Mikrocontroller?

- ·Was ist der Unterschied zwischen STM32CubeMX und STM32CubeIDE?

- ·Wie erkenne ich Objekte mit Kamera im 8051 Mikrocontroller?

- ·Was ist die Rolle der DSP in Machine-Learning- und KI-Anwendungen?

- ·Anwendung von STM32 in digitalen Stromversorgungen

- ·Welcher Mikrocontroller ist am besten, um Motorsprung zu steuern?

- ·Welche Sprache ist am besten für Robotik, IoT, KI, Spiele oder Web-Apps?

- ·Raspberry Pi Pico vs Arduino Nano vs STM32 Blue Pill vs ESP32 vs STM32 Black Pill | Vergleich

- ·Was sind die Fallstricke bei der Konstruktion des STM32-Uhrensystems?