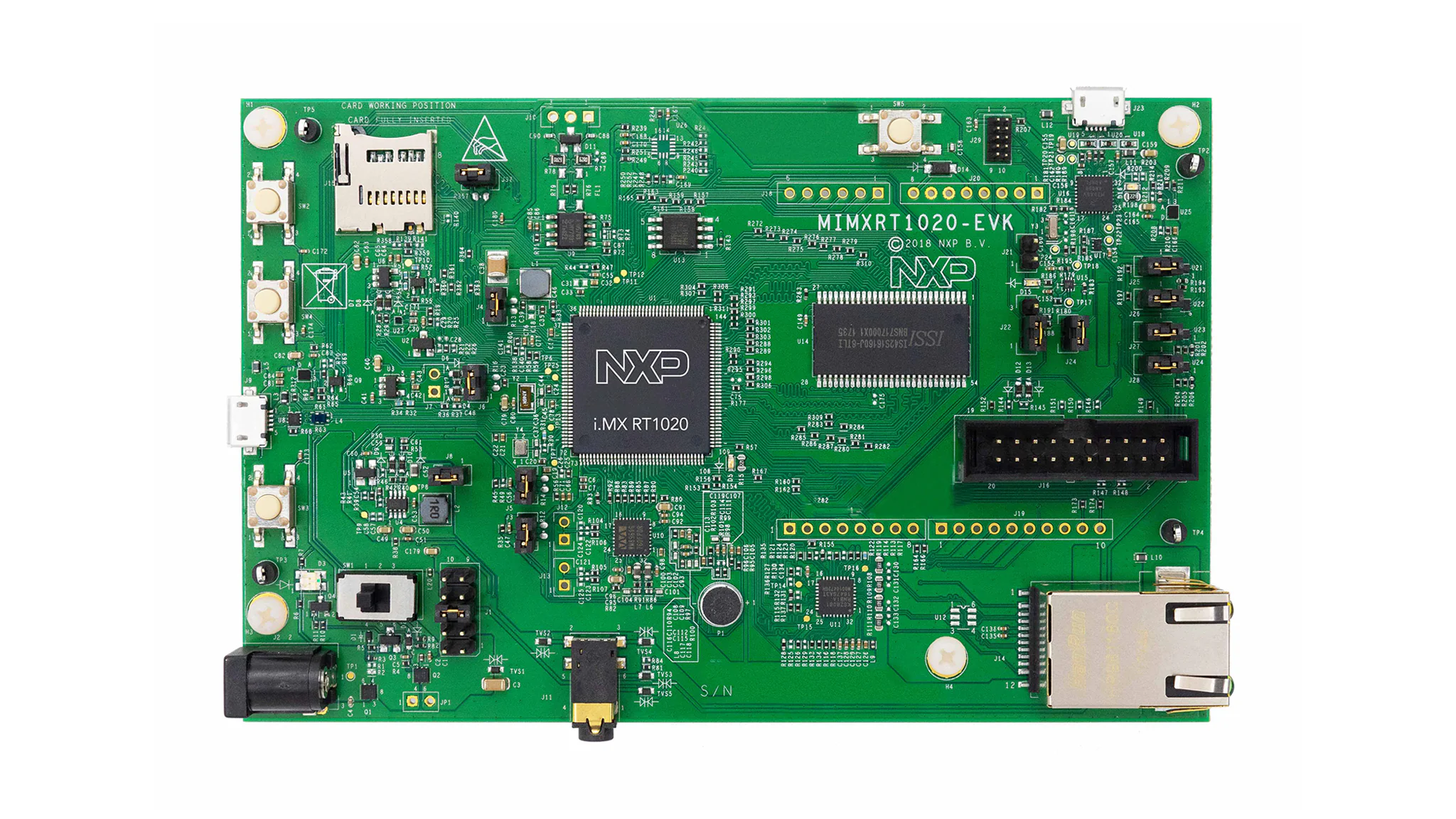

NXP MCU PCB-Layout-Richtlinien für BGA-Gehäuse

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

Das Entwerfen eines PCB-Layouts für NXP MCUs im BGA-Gehäuse (Ball Grid Array) erfordert sorgfältige Planung hinsichtlich Signalintegrität, Stromversorgung und Fertigungsfähigkeit. NXP-Mikrocontroller verfügen oft über fortschrittliche Peripheriegeräte wie Hochgeschwindigkeitsschnittstellen (USB, Ethernet, DDR-Speicher), was Präzision im Layout erfordert.

1. Gehäusedetails und Pre-Design-Checkliste

Verstehen Sie die Parameter des BGA-Gehäuses für den gewählten NXP-Mikrocontroller:

- Ball-Pitch (Rastermaß): Häufige Optionen sind 0,8 mm, 0,65 mm und 0,5 mm für feine Rastermaße.

- Ball-Array-Größe: Bestimmen Sie die Anordnung (z. B. 8x8, 10x10).

- Pads und Vias: Verwenden Sie Via-in-Pad oder Dog-Bone-Fanout für das Escape-Routing.

Checkliste:

- Definieren Sie frühzeitig Ihren PCB-Stack-Up.

- Identifizieren Sie kritische Signale (Hochgeschwindigkeitsschnittstellen wie USB, Ethernet, DDR, SPI).

- Verwenden Sie geeignete PCB-Designtools (Altium Designer, OrCAD, KiCad) mit aktivierten DRC-Regeln.

- Beachten Sie die NXP Hardware Design Application Notes für spezifische Mikrocontroller.

2. Planung des PCB-Stack-Up

Ein gut strukturierter PCB-Stack-Up ist entscheidend für die Stromversorgung, Masseverteilung und Signalführung.

Empfohlener Stack-Up (ab 4 Lagen):

| Lage | Zweck |

|---|---|

| Oberseite | Bauteile, Signal-Routing |

| Lage 2 | Volle Massefläche |

| Lage 3 | Stromversorgungs- oder Signallage |

| Unterseite | Signal-Routing/Bauteile |

- Für 0,8 mm Rastermaß: 4 Lagen sind ausreichend.

- Für feines Rastermaß (0,5 mm): Verwenden Sie 6+ Lagen und HDI-Technologien (High-Density Interconnect) wie Microvias.

3. PCB-Designregeln für BGA-Layouts

Allgemeine Designregeln:

- Leiterbahn-Breite und Abstand:

- 0,8 mm Rastermaß: 4–5 mil Leiterbahnbreite.

- 0,5 mm Rastermaß: 3–4 mil mit Microvias.

- Via-Typen:

- Verwenden Sie Microvias für innere Reihen in feinen BGAs.

- Verwenden Sie Via-in-Pad (gefüllte und verplante Vias), um Induktivität zu minimieren.

- Pad-Größe:

- Für 0,5 mm Rastermaß: ~0,25–0,3 mm Pad-Durchmesser.

- Abstände:

- Halten Sie die Mindestabstände zwischen Pads, Vias und Leiterbahnen gemäß den Fertigungstoleranzen ein.

4. Escape-Routing für BGA

Escape-Routing bezieht sich auf das Herausführen der Signale aus dem BGA-Gehäuse.

Techniken:

- Dog-Bone-Fanout:

- Kurze Leiterbahnen führen von den Pads zu Vias.

- Geeignet für 0,8 mm Rastermaß.

- Via-in-Pad:

- Empfohlen für feine BGAs (≤0,5 mm).

- Erfordert gefüllte und verplante Vias, um Lötfehler zu vermeiden.

Routing-Strategie:

- Äußere Reihen: Direktes Routing auf der Oberseite.

- Innere Reihen:

- Verwenden Sie Microvias oder Blind/Buried-Vias für den Zugriff auf innere Lagen.

- Nutzen Sie Signal- oder Stromversorgungsebenen für dichtes Routing.

Escape-Lagen-Nutzung:

- Verwenden Sie innere Lagen für Stromversorgungs- und Hochgeschwindigkeitssignale, um Rauschen zu reduzieren.

- Verteilen Sie Signale gleichmäßig, um Übersprechen und Engstellen zu vermeiden.

5. Stromversorgungsnetzwerk (PDN)

Ein stabiles Stromversorgungsnetzwerk ist entscheidend für NXP-MCUs, die mehrere Spannungsdomänen besitzen (z. B. VCC, VDDIO, VSS).

Empfehlungen:

- Verwenden Sie solide Masse- und Stromversorgungsebenen, um Impedanz zu minimieren.

- Platzieren Sie Entkopplungskondensatoren nahe an den Stromversorgungs-Pins.

- Niedrige ESR-Keramikkondensatoren (0,1 µF, 1 µF).

- Verbinden Sie Strom- und Masseflächen mit mehreren Vias, um den Stromfluss zu verbessern.

6. Signalintegrität für Hochgeschwindigkeitssignale

Hochgeschwindigkeitssignale wie USB, Ethernet und DDR-Speicher erfordern besondere Layout-Richtlinien.

Wichtige Empfehlungen:

- Impedanzkontrolle:

- Berechnen Sie die Leiterbahnbreite und Abstände für die gewünschte Impedanz (z. B. 50 Ω Single-Ended, 100 Ω differentiell).

- Differential-Paar-Routing:

- Führen Sie Signale wie USB oder Ethernet als symmetrische Paare.

- Gleiche Längen und konsistenter Abstand.

- Längenanpassung:

- Passen Sie die Leiterbahnlängen für Datenleitungen (z. B. DDR) an.

- Übersprechen vermeiden:

- Nutzen Sie Masseflächen oder Abschirmungen zwischen kritischen Signalen.

- Stummel vermeiden:

- Kürzen Sie ungenutzte Pins oder vermeiden Sie lange ungenutzte Leiterbahnen.

7. Wärmemanagement

NXP-MCUs in BGA-Gehäusen erzeugen konzentrierte Wärme, die abgeführt werden muss.

Techniken:

- Platzieren Sie thermische Vias unter dem BGA, um die Wärme auf Masseflächen abzuleiten.

- Nutzen Sie große Kupferflächen um den Mikrocontroller.

- Bei hohen Leistungen: Verwenden Sie externe Kühlkörper mit thermischen Vias.

8. Platzierung von Entkopplungskondensatoren

- Platzieren Sie Entkopplungskondensatoren so nah wie möglich an den Stromversorgungspins.

- Nutzen Sie verschiedene Werte (0,1 µF, 1 µF, 10 µF) für eine optimale Filterung.

- Verwenden Sie kurze Leiterbahnen und direkte Vias zu den Stromversorgungs- und Masseflächen.

9. PCB-Fertigung und Bestückung

- Verwenden Sie solder mask defined pads (SMD) für feine Rastermaße.

- Vermeiden Sie offene Vias unter BGA-Pads, um Lötbrücken zu verhindern.

- X-Ray-Inspektion: Überprüfen Sie die Lötstellen für eine zuverlässige Montage.

10. Designvalidierung

- Führen Sie DRC-Prüfungen (Design Rule Check) durch, um Abstände und Routing zu verifizieren.

- Verwenden Sie Signalintegritätssimulationen (z. B. HyperLynx) für Hochgeschwindigkeitsschnittstellen.

- Analysieren Sie die Stromversorgungsintegrität mit PDN-Tools (z. B. Altium PDN Analyzer).

Zusammenfassung der Checkliste für NXP-BGA-Layouts

- Stack-Up: 4–6+ Lagen für optimale Leistung.

- Escape-Routing: Dog-Bone-Fanout oder Via-in-Pad.

- Stromversorgung: Entkopplungskondensatoren und solide Ebenen.

- Signalintegrität: Impedanzkontrolle und Differential-Paar-Routing.

- Wärmemanagement: Thermische Vias und Kupferflächen.

- Fertigung: SMD-Pads und X-Ray-Inspektion.

Durch Befolgen dieser Richtlinien erstellen Sie ein zuverlässiges und leistungsstarkes PCB-Layout für NXP-MCUs im BGA-Gehäuse.